- 您现在的位置:买卖IC网 > Sheet目录479 > MRF49XAT-I/ST (Microchip Technology)IC RF TXRX 433/868/915 16-TSSOP

�� �

�

�

�MRF49XA�

�2.17�

�Control� (� Command� )� Register� Details�

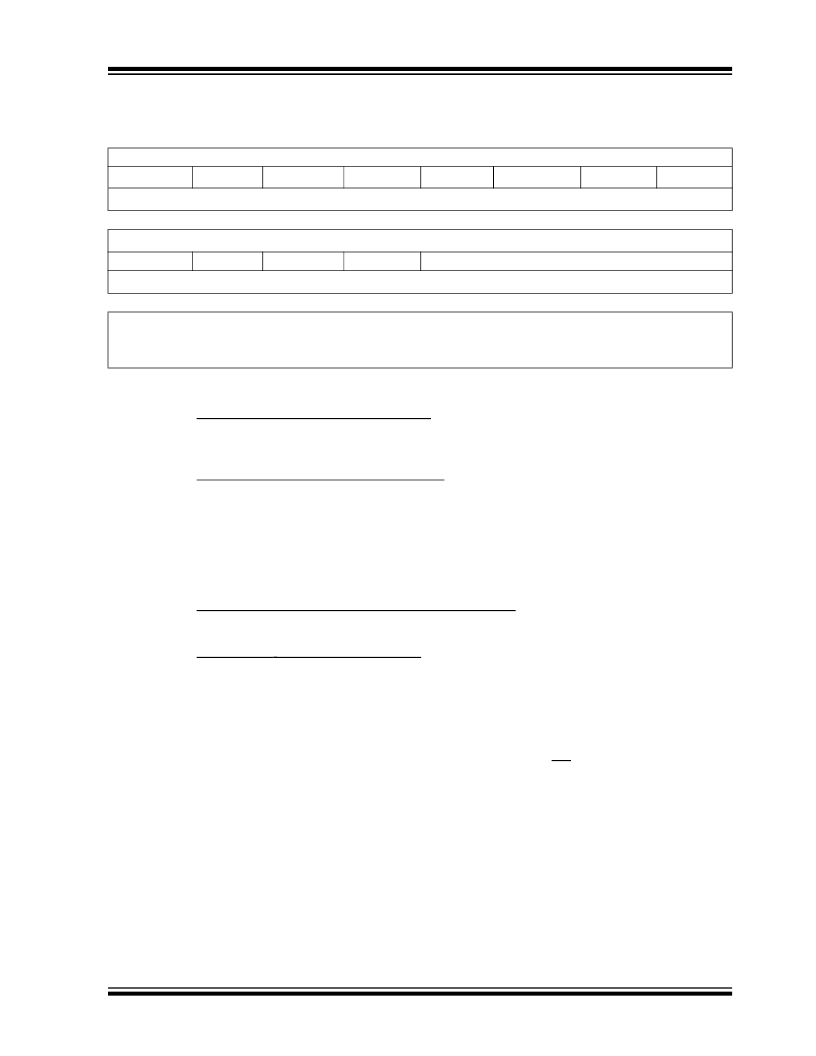

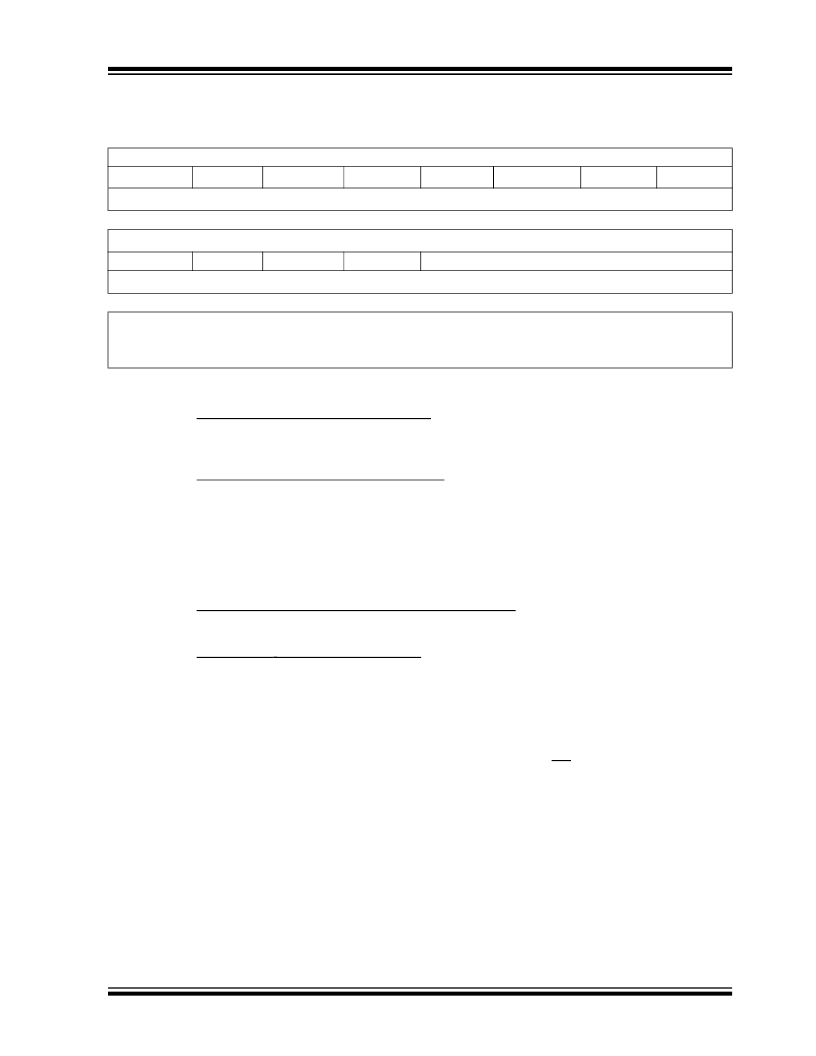

�REGISTER� 2-1:�

�STSREG:� STATUS� READ� REGISTER� (POR:� 0x0000)� (1)�

�R-0�

�TXRXFIFO�

�R-0�

�POR�

�R-0�

�TXOWRXOF�

�R-0�

�WUTINT�

�R-0�

�LCEXINT�

�R-0�

�LBTD�

�R-0�

�FIFOEM�

�R-0�

�ATRSSI�

�bit� 15�

�bit� 8�

�R-0�

�R-0�

�R-0�

�R-0�

�R-0�

�R-0�

�R-0�

�R-0�

�DQDO�

�CLKRL�

�AFCCT�

�OFFSV�

�OFFSB<3:0>�

�bit� 7�

�Legend:�

�r� =� reserved� bit�

�bit� 0�

�R� =� Readable� bit�

�W� =� Writable� bit�

�U� =� Unimplemented� bit,� read� as� ‘0’�

�-n� =� Value� at� POR�

�‘1’� =� Bit� is� set�

�‘0’� =� Bit� is� cleared�

�x� =� Bit� is� unknown�

�bit� 15�

�bit� 14�

�bit� 13�

�bit� 12�

�bit� 11�

�Note� 1:�

�2:�

�3:�

�4:�

�5:�

�TXRXFIFO:� Transmit� Register� or� Receive� FIFO� bit�

�Transmit mode: Transmit Register Ready bit� (2)�

�Indicates� whether� the� transmit� register� is� ready� to� receive� the� next� byte� for� transmission.�

�1� =� Ready� (5)�

�0� =� Not� ready�

�Receive mode: Receive FIFO Fill (Interrupt) bit� (2,3)�

�Indicates� whether� the� RX� FIFO� has� reached� the� preprogrammed� limit.�

�1� =� Reached� the� preprogrammed� limit� (5)�

�0� =� Programming� limit� has� not� been� reached�

�POR:� Power-on� Reset� bit�

�1� =� POR� has� occurred� (5)�

�0� =� POR� has� not� occured�

�TXOWRXOF:� Transmit� Overwrite� Receive� Overflow� bit�

�Transmit mode: Transmit Register Underrun or Overwrite bit�

�1� =� Underrun� or� overwrite� (5)�

�0� =� Operating� normally�

�Receive mode� :� Receive FIFO Overflow bit�

�1� =� FIFO� overflow� (5)�

�0� =� Operating� normally�

�WUTINT:� Wake-up� Timer� (Interrupt)� Overflow� bit�

�1� =� Timer� overflow� has� occurred� (5)�

�0� =� Operating� normally�

�LCEXINT:� Logic� Change� on� External� Interrupt� bit�

�Indicates� a� high-to-low� logic� level� change� on� external� interrupt� pin� (INT/DIO)� (5)� .�

�1� =� High-to-low� transition� has� occurred�

�0� =� High-to-low� transition� has� not� occured�

�All� register� commands� begin� with� logic� ‘� 1� ’� and� only� the� STATUS� register� read� command� begins� with� logic� ‘� 0� ’.�

�This� bit� is� multiplexed� for� Transmit� or� Receive� mode.�

�See� the� FFBC� bits� (FIFORSTREG<3:0>)� in� Register� 2-10� .�

�To� get� accurate� values,� the� AFC� should� be� disabled� during� the� read� by� clearing� the� FOFEN� bit�

�(AFCCREG<0>).� The� AFC� offset� value� (OFFSB� bits� in� the� status� word)� is� represented� as� a� two’s�

�complement� number.� The� actual� frequency� offset� can� be� calculated� as� the� AFC� offset� value� multiplied� by�

�the� current� PLL� frequency� step� from� CFSREG� (FREQB<11:0>).�

�This� bit� is� cleared� after� STSREG� is� read.�

�?� 2009-2011� Microchip� Technology� Inc.�

�Preliminary�

�DS70590C-page� 19�

�发布紧急采购,3分钟左右您将得到回复。

相关PDF资料

MRF89XA-I/MQ

TXRX ISM SUB-GHZ ULP 32QFN

MRF89XAM9A-I/RM

IC TXRX MOD 915MHZ ULP SUB-GHZ

MRX-001-433DR-B

MODULE RECEIVER 433MHZ 18DIP

MRX-002-433DR-B

MODULE RECEIVER 433MHZ 18DIP

MRX-002SL-433DR-B

MODULE RCVR 433MHZ SAW LN 24DIP

MRX-005-915DR-B

MODULE RECEIVER 915MHZ 18DIP

MRX-005SL-915DR-B

MODULE RCVR 915MHZ SAW LN 24DIP

MRX-007-433DR-B

MODULE RECEIVER 433MHZ 18DIP

相关代理商/技术参数

MRF49XAT-I/T

制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:ISM Band Sub-GHz RF Transceiver

MRF49XAT-I-ST

制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:ISM Band Sub-GHz RF Transceiver

MRF49XAT-I-T

制造商:MICROCHIP 制造商全称:Microchip Technology 功能描述:ISM Band Sub-GHz RF Transceiver

MRF4A(AMMO)

制造商:Bel Fuse 功能描述:FUSE

MRF5

制造商:Ferraz Shawmut 功能描述:

MRF50

制造商:Ferraz Shawmut 功能描述:

MRF500

制造商:Ferraz Shawmut 功能描述:

MRF5003

制造商:MOTOROLA 制造商全称:Motorola, Inc 功能描述:N-CHANNEL BROADBAND RF POWER FET